오늘은 4장 뒷부분

오늘 할 내용은 Logic Microoperations, 저번에는 4가지 유형 중 1,2번째를 했고

오늘 3,4번 유형에 대해 살펴볼 것

Logic microoperations를 처리할 때에는 주어진 레지스터에 있는 데이터들의 각 비트를 개별적으로 처리를 해주어야한다. 예를 들어서, P : R1 <- R1 XOR R2 ; 세부적으로 보면 P는 조건, 조건에 만족하면 우측에 있는 오퍼레이션을 동작(R1 XOR R2) 그것을 R1으로 저장.

두 번째 예제 P+Q : R1 <- R2 + R3, 조건이 P+Q인데 조건에서의 +는 OR Gate로 표현, 즉 둘 중 하나만 참이면 조건에 만족, 대신 오른쪽에 나오는 +는 ADD를 의미. 오른쪽에서의 OR는 V형태로 표현한다. 조건에서의 OR와 오퍼레이션에서의 OR 기호 표현이 다르므로 기억할 필요가 있다.

# 16개의 논리 마이크로연산과 그거에 대한 진리표를 한 번씩 비교해보면서 기호를 숙지하고 이해를 하자

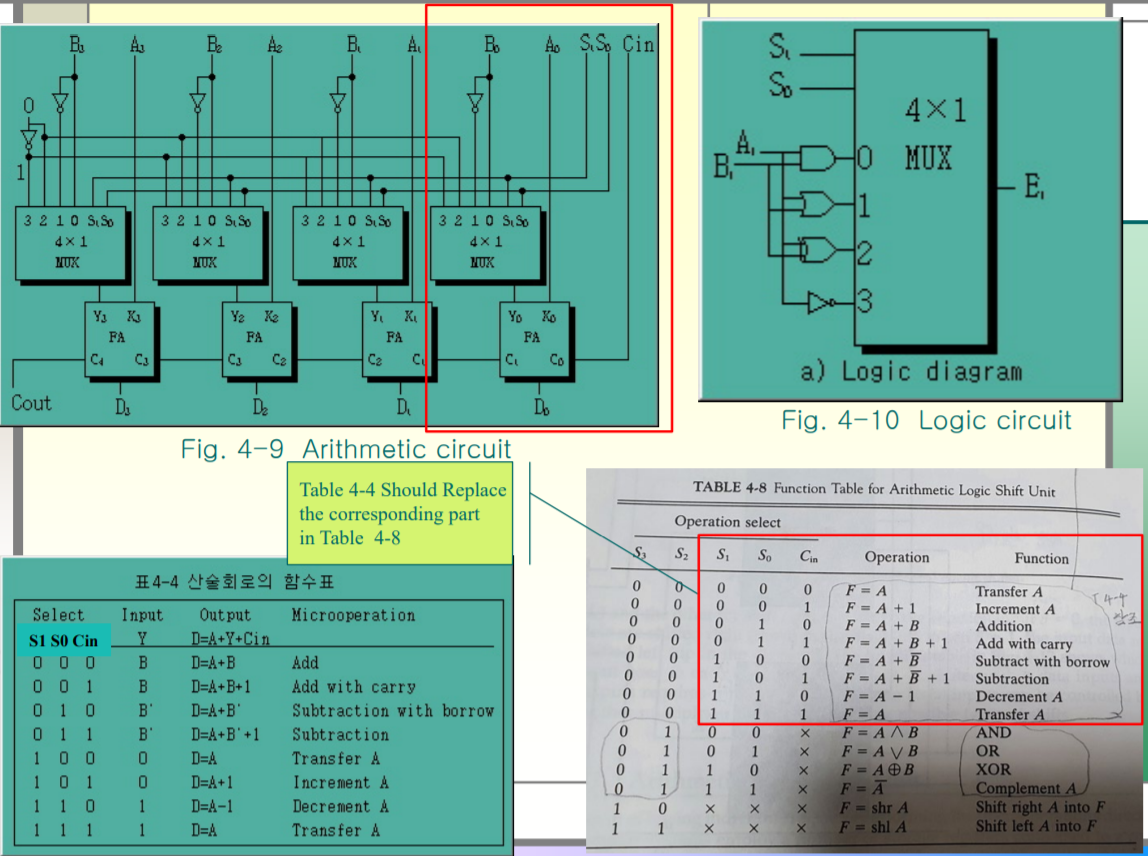

이제 하드웨어 적으로 어떻게 구현을 할 수 있는지 설명

위에서 16개의 연산에 대해 진리표와 함수식을 보았는데 가장 많이 사용하는 것은 AND, OR, XOR, Complement

4개를 가장 많이 사용하므로 4X1 MUX를 이용한다. 0번 채널은 AND, 1번 게이트는 OR, 2번 채널은 XOR, 3번 채널은 NOT게이트, 입력값이 4개이므로 Select 2개, Select 단자가 무엇이냐에 따라 입력값이 달라짐(중간고사 범위)

a)는 한 비트에 대해서만 보여주고 있는 것, 그래야 만약 n비트짜리 logic operations을 수행하는 H/W를 만들겠다고 하면 위와 같은 것이 n개 있어야 한다는 것을 의미한다.

여기서는 추가적인 예시를 보여준다. 하고자 하는 것은 특정 레지스터 안에 들어간 값을 1로 만들어준다, complement시켜준다, 0으로 clear시켜준다, 특정 비트 값을 우리가 원하는 값으로 바꿔준다 등 이런 작업을 할 수 있다는 것을 보여줌

그래서 우리가 갖고 있는 데이터가 A(processor register)안에 들어가 있는 것이고, B라는 레지스터에서는 logic operand값, 즉 어느 비트 어느 비트 값을 바꿀거냐, 비트 위치에 해당되는 정보를 갖고 있음.

첫 번째 예시는 Selective-set, A(1010)에서 특정위치의 값을 무조건 1로 만들라는 예시 ex) 첫번째와 두번째 비트값을 1로 바꾸려면 or를 통해 변경 할 수 있다

두 번째는 Seletive_complement, Complement를 할 때는 XOR를 이용해서 가능

세 번째는 Seletive_clear, clear이므로 원하는 위치에 있는 값을 모두 0으로 바꾸겠다-> B를 complement한 후 and operation을 취하면 앞에 있는 두 비트를 모두 0으로 변경하도록 할 수 있다.

네 번째는 Insert(MASK & OR) : 주어진 게 있고, 그것을 변경을 해서 최종적으로 이렇게 만들고 싶다 이런 의미, 위의 그림에서 보면 want값이 나옴.

Insert Operation은 2단계를 거쳐 수행한다.

1) MASK : 위에서 살펴본 특정 위치의 값을 0으로 변경

2) 우리가 원하는 값을 만들 수 있도록 OR를 이용한다

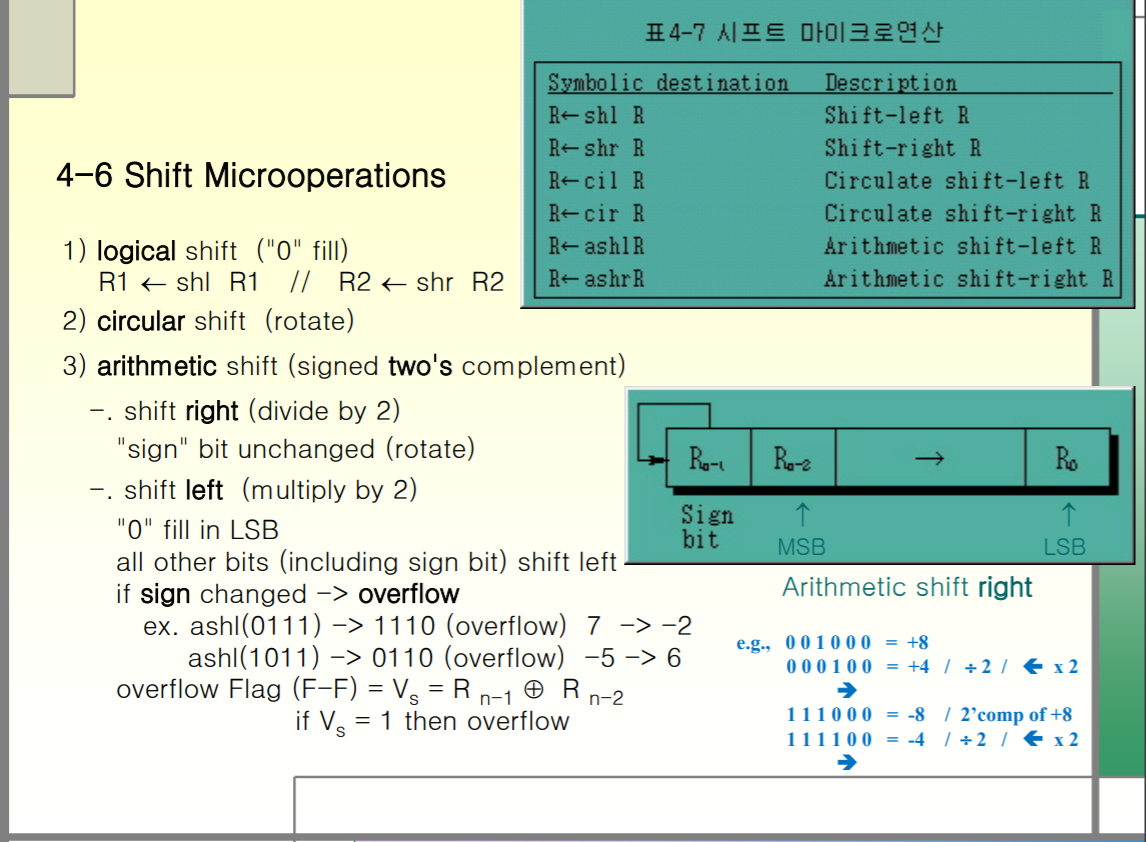

이제 나오는 것은 Shift Microoperations, 종류가 세 가지.

1) logical shift (제일 단순, 왼쪽/오른쪽으로 한 비트씩 이동, 밀려서 밖으로 튕겨져나가면 반대편은 0으로 채워짐)

2) circular shift (순환 구조, 가장자리 비트가 밀려서 밖으로 나가면 다시 반대편으로 되돌아서 들어옴) 만약 8비트짜리가 한 방향으로 8번 shift하게 되면 본래 모습과 동일

3) arithmetic shift (왼쪽으로 shift, 오른쪽으로 shift 방법이 조금 다름)

shl - 왼쪽으로 shift

shr - 오른쪽으로 shift

cil - 왼쪽으로 circular shift

cir - 오른쪽으로 circular shift

ashl - arithmetic 왼쪽으로 shift

ashr - arithmetic 오른쪽으로 shift

arithmetic shift를 보면 signed two's complement라고 되어있음, 위에 그림을 보면 가장 왼쪽 비트는 sign 비트임, 0은 양수 1은 음수 나머진 숫자들

만약 ashr을 하게 되면 siged bit는 계속 같은 값으로 유지, 나머지는 한 비트씩 오른쪽으로 밀려가고 맨 오른쪽 비트는 빠져나감, 이 경우에는 2로 나눈 효과를 줌, ashl은 2를 곱하는 효과를 줌, 대신 왼쪽으로 shift하는 경우 sign비트로도 밀려가고 바깥에서도 들어옴, sign비트 바로 옆 비트를 MSB라고 한다(가장 중요한 비트 - 큰 가중치를 가지고 있기 때문)

ashl은 sign비트로도 밀리기 때문에 signed 비트가 바뀌는 경우가 생긴다, 이걸 overflow가 발생했다고 표현한다.

ex) 0111 : ashl-> 1110 (overflow) 7 -> -2, 1110은 음수이고 이것의 2의 보수를 취하면 -2

1011 : ashl -> 0110 (overflow) -5 -> 6

overflow가 발생하는 지 쉽게 알 수 있는 방법은 왼쪽의 비트 2개를 XOR했을 때 1이 나오는 경우 ashl을 수행하면 overflow가 발생한다.

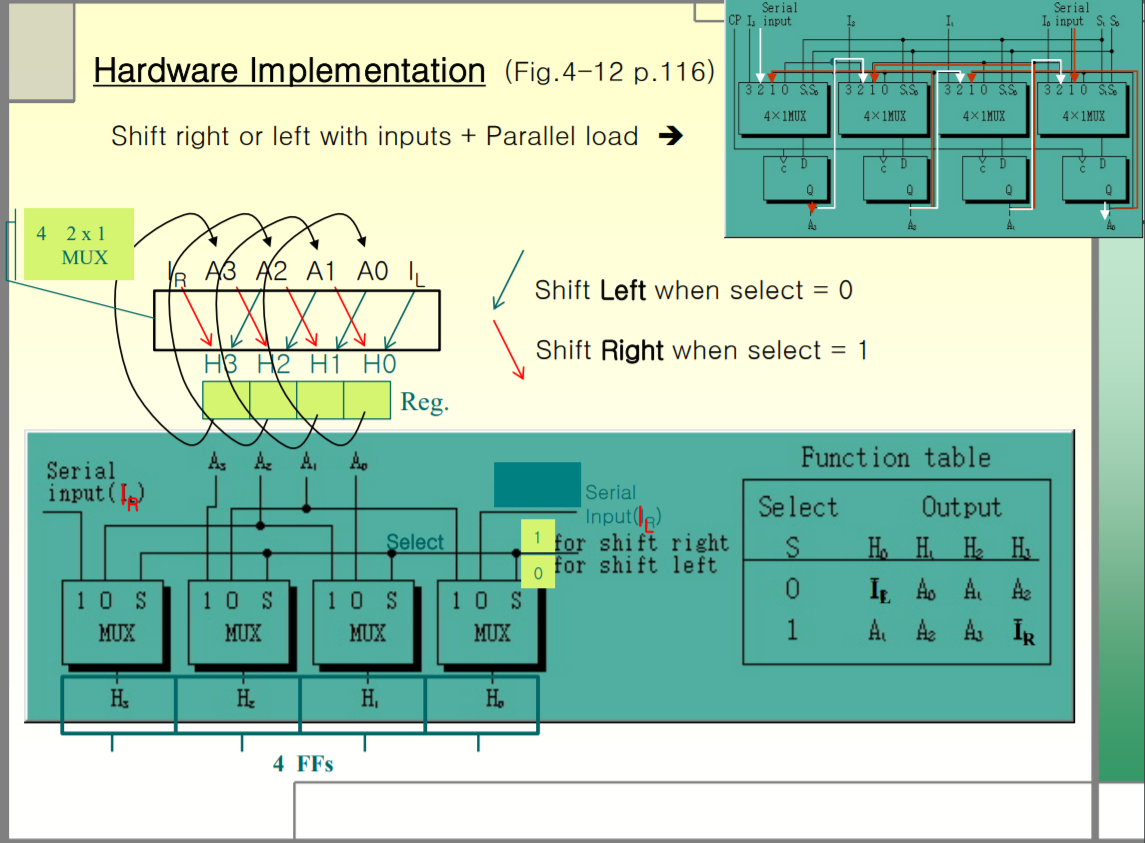

Hardware Implementation - 위 그림에 4개의 FF이 추가가 된 것은 교과서 내용이 단순하면서도 이해하기 쉽지 않아 교수님이 직접 추가하신 것이다. 오른쪽 위에 있는 그림은 shift register이다. (하얀색 선은 right shift, 빨간색 선은 left shift) 4X1 MUX를 통해 선택적으로 left/right shift operations을 수행 <- 기본적인 구조

밑의 그림도 의미는 비슷, 위에 4x1 MUX는 외부에서도 들어오고 추가적인 기능이 있기 때문에 4x1 MUX를 사용했지만

아래 그림은 left / right 밖에 선택사항이 없기 때문에 2x1 MUX를 사용한다. 만약 0번 채널이 선택되면 left shift를 수행

처음에 0번 채널에는 Serial Input값으로 1이 들어오는 거처럼 생각할 수 있지만 1이 들어오는게 아니다. 이건 MUX이기 때문에 출력 그 이후에 FF이 있어야한다. 그래서 FF을 그려주신 것. 그래놓고 0번 채널이 선택 됐으니까 외부에서 1이 들어오고 FF에 있는 값은 옆으로 이동한다. 옆으로 가는데 더 위에 그림에 있는 것처럼 한 바퀴 돌아서 A0로 연결되고 그것이 0번채널로 들어간다. 그리고 그 값이 H1으로 간다. H1도 마찬가지로 한 바퀴 돌아서 A1으로 들어가고 그것이 H2로 들어간다. 즉 0번 채널이 선택되면 left shift operation을 수행하게 된다. 위에 한 바퀴 돌아가는 듯한 그림을 보면 이해하기 쉽다. 마찬가지로 right shift operation은 1채널이 선택되면 수행하게 된다.

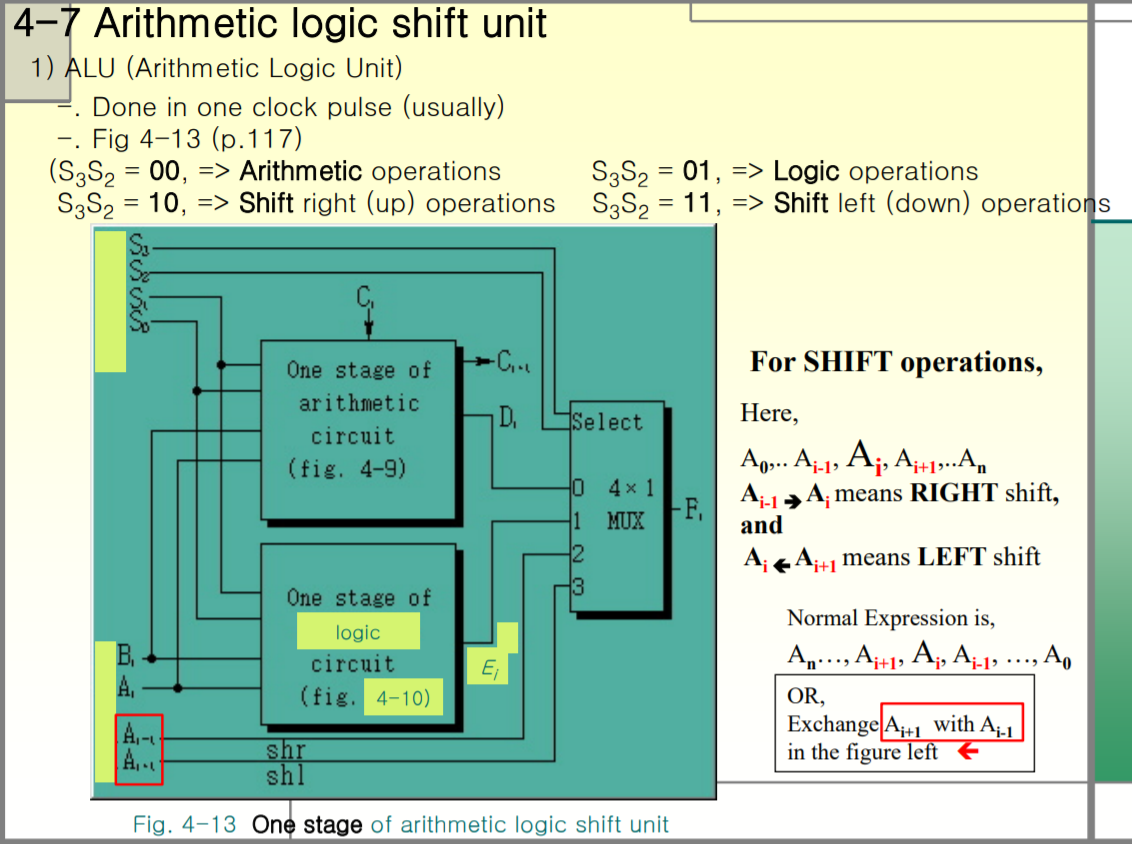

4-7절은 Arithmetic logic shift unit

우선, 이 구조를 크게 보면 위에 있는 block(4-9)은 하나의 stage가 block diagram안에 있다는 것을 뜻한다.

4-9는 바로 아래 그림의 사각형 부분, 근데 아래 그림은 4비트짜리인데 그 중에 하나의 4x1 MUX와 FA가 하나의 pair로 한 비트에 해당하는 부분이다. 즉, 한 비트의 부분이 4-9 block diagram

아래의 logic circuit에 해당하는 4-10 diagram은 아래 오른쪽 그림이다. 위에서 배웠던 4가지 operation에 해당하는 그림이다. 이것 자체가 1bit용 Hardware이다. (Ai에 해당하는 하나의 비트)

그리고 shift operation에 해당하는 것이 아래의 Ai+1과 Ai-1에 해당하는 것.

가장 오른쪽의 4x1 MUX를 보면 Select bit 2개가 S2, S3값으로 들어온다. 즉 S2, S3값이 뭐냐에 따라서 { 0, 1, 2, 3 } 4개의 값 하나가 선택이 되고 그 값이 어디에 연결되어있느냐에 따라 다르게 수행한다.

ex) s2, s3가 00이면 0번 채널이 선택되고 그것은 arithmetic을 통해 들어오므로 +, -연산을 수행 s3, s2가 01이면 1이 선택 되어 logic연산 수행, 그리고 2, 3이 선택되면 shift연산을 수행한다.

Ai-1에서 Ai로 이동하는 것은 right shift를 의미

Ai+1에서 Ai로 이동하는 것은 left shift를 의미, 하지만 이와 같은 표현 방식은 일반적이지 않다. 왜냐하면 Normal Expression이 An ,,, Ai+1, Ai, Ai-1, ,,, , A0으로 표현하기 때문에 위처럼 표현하면 반대가 된다. 이걸 방지하기 위해서는 위 그림의 빨간 박스 모양 Ai-1과 Ai+1을 바꿔주던지 shr 또는 shl을 바꿔주던지 해야한다.

빨간 박스 모양은 잘못 나온것, 왼쪽의 함수표가 빨간 모양으로 들어가는 것이 맞는 함수표