Basic Computer를 어떻게 설계하는지 그에 대한 과정

위 슬라이드는 컴퓨터를 구성하는 하드웨어 구성요소에 대한 설명이다

4096 X 16 : 12비트 주소면 메모리를 주소가지고 접근할 수 있다

9개의 레지스터

7개의 FF (I - 주소 방식 결정, S - Start/Stop, E - overflow 또는 carry, R - interrupt, IEN - IEN이 1이면 interrupt가 들어왔을 때 받아주는 것, 0이면 들어와도 받아주지 않음, FGI/FGO - 입출력 flag)

Decoder : 오른쪽 그림 위 / 아래

Common Bus : 왼쪽 그림 테두리

Control logic : 오른쪽 그림 Control Logic gates

Adder & logic : 왼쪽 그림 AC 왼쪽 Adder and Logic

전 강좌에서 설명했었던 것에 대한 세부설명그림 - 오른쪽 그림에 대한 상세한 설명은 하지 않음

Control Logic Gates를 어떻게 설계해야하는지에 대한 설명

우선 Input과 Output에 대한 설명

Input : 2개의 Decoder에 대한 출력값이 입력값으로 들어옴 등등 위에 적혀있는 것들

Output :

signals to 9 registers ; 원하는 기능을 수행할 수 있도록 9개의 레지스터 출력값 나와야한다

signals to memory ; memory가 수행할 작업에 대한 것

signals to 7 F-F

signals to BUS

signals to adder and logic circuit

위 슬라이드는 AR을 제어하는 것들에 대한 설명

5가지 중 위에 3개는 Load와 관련된 제어이고, RT0는 0으로 Clear시키는 제어, 제일 마지막은 increment제어이다.

첫번째는 위위 슬라이드 가장 맨 위 Fetch에 대한 것

3가지 Load 관련 제어가 OR Gate로 제어된다 하나라도 만족하면 LD가 1로 된다.

뿐만 아니라 Read. Write Memory에 관한 것들로 위 슬라이드처럼 묶을 수 있다. 위 하얀 페이지에서 각각 해당하는 것을 찾아(Read : <- M[AR] / Write : M[AR] <-) 식으로 나타내어주면 된다.

이렇게 Register와 Meomory를 어떻게 제어하는지 알 수 있다.

Control of Sigle F-F's의 하나의 예

IEN의 set 또는 clear에 관한 것을 연산식 및 회로로 설명한 것

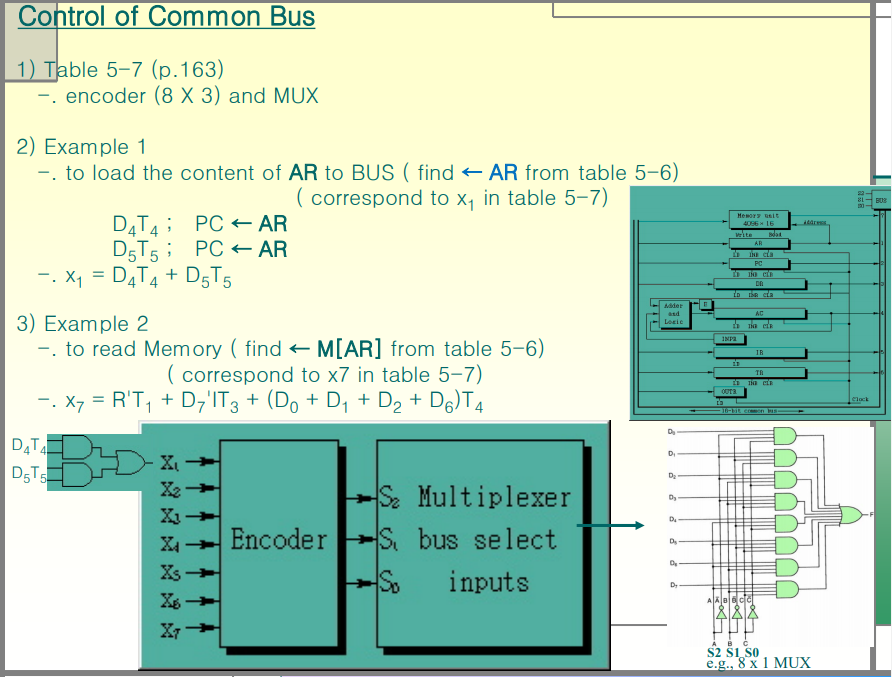

Example 1)은 AR이 BUS를 쓴다는 것이고 이것에 대한 식을 표에서 찾아보면 위 처럼 D4T4 + D5T5가 된다.

이는 And 게이트 2개, Or 게이트 1개로 묶여있고 아래 그림으로 표현되어있다. 만족하면 1이 X1으로 들어가고 그것이 Encoder로 들어간다. 나머지는 다 0 그럼 출력값은 S2 = 0, S1 = 0, S0 = 1로 된다. 이 3가지 + Address Register 한 비트가 And게이트로 들어가 출력값이 BUS에 해당하는 비트 값이 나온다. 오른쪽 회로가 16개있다고 하면 16비트 BUS가 있다는 것

AC에 해당하는 (AC가 dest가 되는) 조건 및 식을 찾아보면 위처럼 나타낼 수 있다. 총 9개

처음 7개는 LD, 8번째는 Clear, 맨 아래는 Increment에 해당

각 기능에 해당하는 식들을 취합하여 식 및 회로에 대한 슬라이드

ex) D1T5 : 출력값이 1 나오면 ADD 조건에 만족, 그러면 From Adder and Logic부분에서 더해지고 그것을 AC가 받아들인다. AC가 받아들이기 위해 LD가 1이어야한다.

이런 식으로 각각의 기능 조건에 만족하면 LD와 연결되어 기능 수행

INC와 CLB는 각기 다른 선으로 연결 및 기능 수행

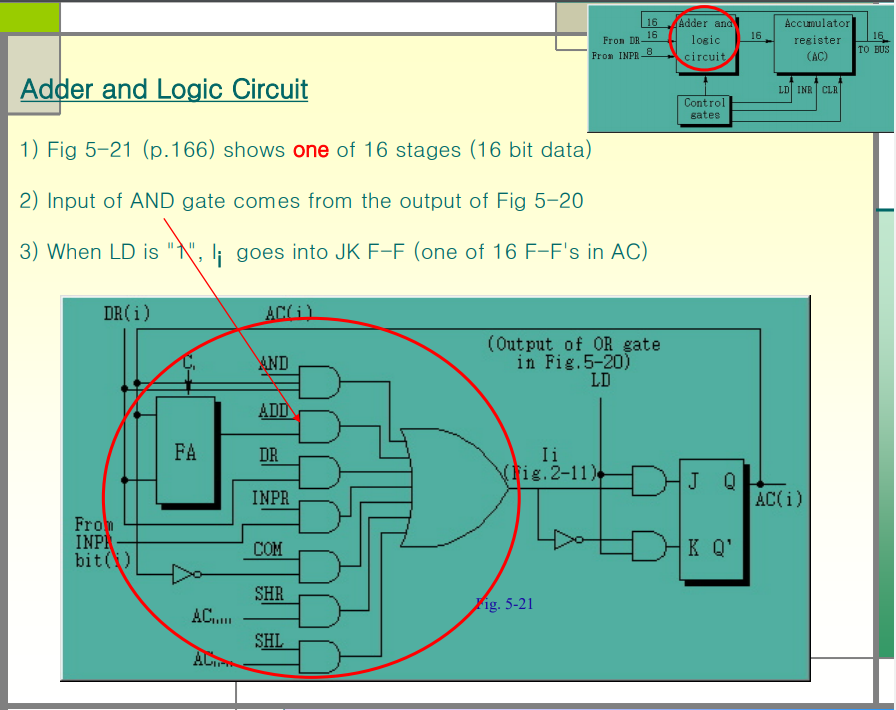

위에서 설명한 AC 전에 연결되어있는 Adder and Logic Circuit 부분

Adder and Logic의 입력값은 Speical Path로 연결된 AC의 값, DR, INPR의 값이다.

아래 회로에서 AND게이트에 연결되어있는 AND, ADD, DR 등등은 전 슬라이드와 같은 이름에 해당하는 부분이 조건에 만족하여 나온 것과 연결되어있는 것

AND는 전 슬라이드 AND조건에는 이미 충족한 상태이고 AC의 값, DR의 값이 입력값에 해당한다. 이 값들로 Logical AND GATE를 통과한다

ADD는 FA를 이용, FA의 입력값은 AC의 값 하나 + DR의 값, FA를 통과시켰기에 SUM, CARRY가 존재하는데 SUM의 값을 ADD와 Logical AND GATE로 통과시킨다. 만약 SUM값이 1면 AND 게이트를 통과한 값도 1이 되고 그 값이 JK F/F에 들어가야한다. (J=1, K=0) 만약 SUM값이 0이 된다. 그러면 출력값이 0이 되고 K단자에는 NOT게이트를 통과하여 1, J단자에는 0이 들어가(J=0, K=1) F/F의 다음 상태값은 0이 된다.

DR은 AC에 값을 전달해주면 되는 것. DR값이 1이면 다음 상태를 1, 0이면 다음 상태 CLEAR

나머지도 다 똑같이 수행

전체적인 구성과 그 세부 회로

우리가 지금까지 한 게 각종 하드웨어들을 제어하는 것