오늘부터 시작해서 2장을 들어감

1장에서는 조합회로, 순차회로, 어떻게 설계하는지에 대해서 배웠고, 2장에서는 설계된 회로들을 Digital Components라고 IC칩에 대해서 배울 것. 어떤 것들이 많이 쓰이며, 그들의 구조가 어떻게 되는지, 어떻게 사용되는지

2-1. IC칩이 어떤 형태로, 어떠한 장점을 갖고 있는지, 어떠한 과정으로 만들어지는지

IC 칩의 장점 :

첫 번째, 사이즈가 작고, 비용이 적게 들며, 열의 발생량을 줄일 수 있으며 신뢰도는 높아진다. 또한 운영 속도는 증가한다.

크기로 가지고 분류할 수 있는데 분류 기준은 IC칩에 들어가는 로직 회로들의 개수로 분류 할 수 있다.

SSI : IC칩에 들어가는 로직 회로들이 수십개인 경우

MSI : 수백개

LSI : 수천개

VLSI : 수천개 이상 ~

일반적으로, IC칩의 사이즈는 어느정도 되지만, 회로 자체가 차지하는 부분은 굉장히 작다. 입력 신호는 들어가야하고 출력 신호는 나와야하기 때문에 그것들을 위한 핀들이 여러개 꽂혀있다. (양쪽)

결론적으로, 칩 자체는 공간을 많이 차지하지 않지만 입력/출력 신호값을 위한 핀들에 의해 사이즈가 칩보다는 크다.

공정 : IC칩을 만들기 위해서 공정 분류

TTL : 트랜지스터 - 트랜지스터 - 로직 -> 가장 많이 쓰이는 방식

ECL : 속도가 빠른 장점을 갖고 있다 ex) Super Computer

MOS : 밀도가 높다. (정해진 공간 안에 더 많은 데이트 삽입 가능)

CMOS : 열의 발생량이 적다.

2-2 Decoders (해석하다, 해독하다)

1) 한 코드에서 다른 코드로 변환시켜주는 역할을 한다 ex) 위 그림에서 입력으로 들어온 3비트 짜리 2진수 입력값을 8비트짜리(8진수) 출력값으로 변환시켜주었다. 2진수 -> 8진수

2) 입력으로는 n비트짜리 binary code를 받고 2^n의 출력값이 나온다.

3) n to m decoders : n개의 입력, m개의 출력으로 구성되고 n X m decoder라고 얘기한다.

E -> Enable단자는 ON/OFF Switch라고 작용. E값이 1이면 동작하기 시작,

--->>>> 위 그림에 대해서는 직접 해보는게 더 도움이 될 것 같다.

마지막 2 x 4 decoder, 4 x 16 decoder는

2x4 decoder : 입력이 2, 출력이 4 or 2비트 짜리 이진수를 4진수로 변경

4x16 decoder : 입력 신호값은 4개 출력 신호값은 16

어떻게 동작을 할까? 바로 전에 본 decoder와 반대로 동작함

일단 왼쪽 아래에 있는 Enable단자를 보면 Not게이트가 붙어있다. 이 말은 즉슨, E에 0이 입력으로 들어와야 Not게이트를 거쳐 1로 된다. Enable단자에 1이 들어오면 결과적으로 0이 되기 때문에 마지막에 NAND게이트에 의해 어처피 모두 1이 될 것이다.

똑같이 Enable단자를 이용

입력은 3비트인데 2x4 decorder밖에 주어지지 않았으므로 A0, A1을 입력값으로 두고 A3는 Enable로 사용함으로써 입력값을 준다. A3 = E을 0일 경우와 1일 경우로 나누어 위에 있는 decorder로 들어갈지, 아래에 있는 decorder에 들어갈지 결정되고 출력값은 각각 4개씩 나오므로 총 8개가 나올 수 있는 것이다. 위에 그림과 오른쪽 표를 이용하여 이해해보자

밑에 예제는 영상으로 이해해보자.

다음으로 나오는 것이 Encoder : Encoder는 decoder 정반대 동작을 함

Encoder의 주된 목적 : 어느 값이 1이라는 값을 가지고 Encoder에 입력으로 들어왔는지에 따라서 그거에 대한 이진수 코드를 만들어내는 것. 회로로 만들 때는 or게이트 3개면 충분 (위 그림에 대한 식은 아래 식으로 나타내어줌)

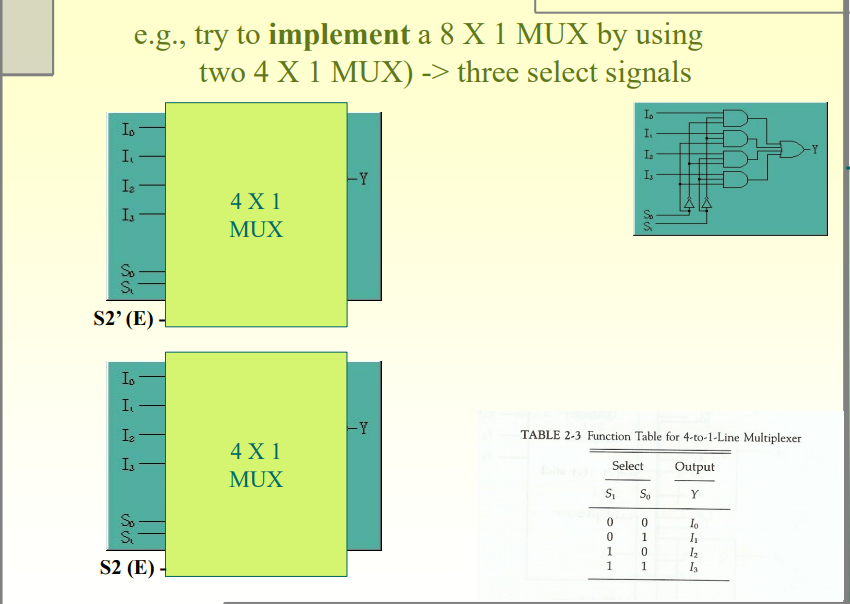

multiplexer(MUX) or 4-to-1 line selector : 4개의 입력신호/라인 중에서 한 채널만 선택해서 출력으로 내보낸다.

4개의 입력 값 중 하나를 선택해주어야하기 때문에 밑에 줄에 있는 Select Bit를 사용, 4는 2비트만 있으면 됨(4 = 2^2)

오른쪽 Table의 세번째를 보면 S1 = 1, S2 = 0 일 때 출력값은 I(2)이다 확인해보면

아래 S1이 1일 경우 I2의 가운데로 들어가게 되고, S0이 0이면 Not게이트를 거쳐 I(2)의 맨 아래에 들어가게 된다.

즉, s1, s2모두 1의 값으로 AND 게이트로 들어가게 되므로 I(2)의 입력값이 그대로 출력값으로 나오게 된다.

입력이 8이므로 입력 채널이 8개이다(위 아래 4개씩) 하지만 Select bit는 위에서 사용하던 4x1 mux의 2개밖에 없다

그런데 8개 중에 1개를 선택하려면 Select bit는 3개가 필요. 그래서 S2(E)를 Enable단자에 추가된 것이다.

입력채널은 전부 8개, S값이 뭐냐에 따라서 S2값이 0이면 위에 mux는 꺼져있고 S2값이 1이 되면 아래 mux는 켜져있게 된다. 그래서 S2값이 1일 때 나머지 입력값들이 뭐냐에 따라서 line을 선택하는 것이다.

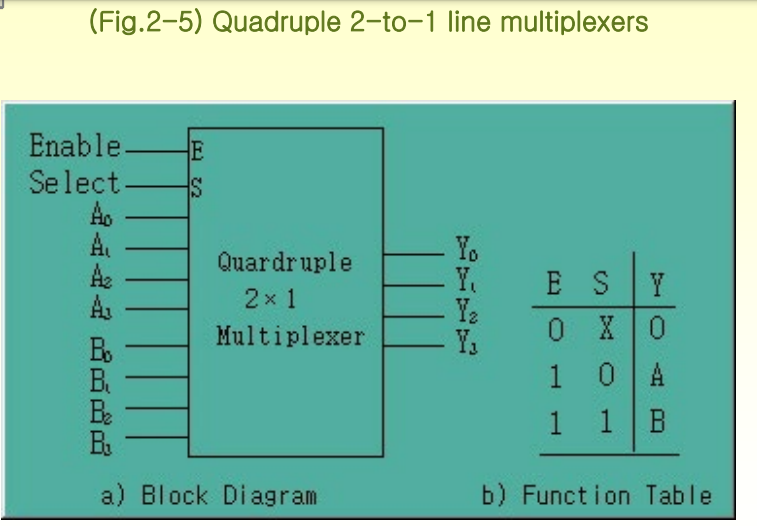

입력 2개 중 1개만 선택하므로 Select도 1개만 존재. 그렇게 동작하기 위해서 당연히 Enable이 1이여야 켜져있으므로 동작, 0은 꺼져잇으므로 동작 x

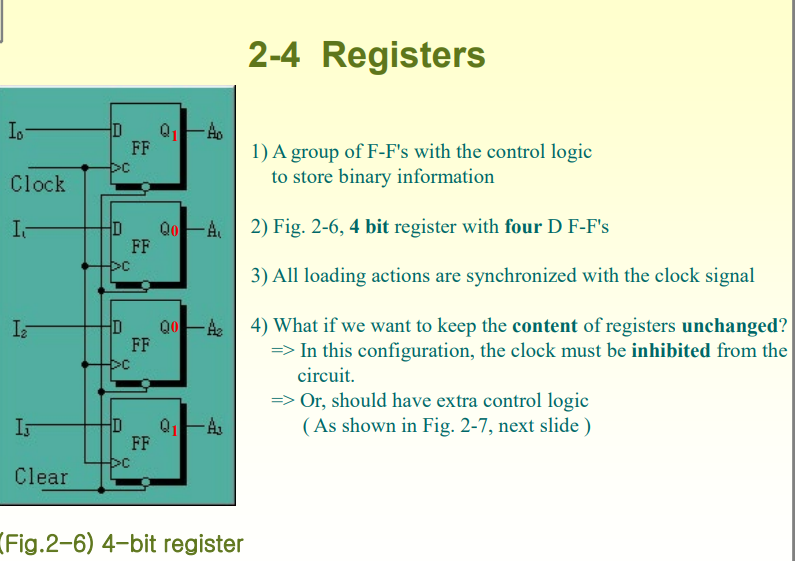

2-4 Registers

: Flip-Flops여러 개로 이루어진 것, 아래 그림은 4비트 정보 저장을 위해 Flip-Flops 4개로 이루어진 레지스터

Clock값에 의해 동기화.

설명부터 적자보면, D F/F이므로 입력값에 의해 결과값이 변경된다. 만약 D F/F 입력값으로 1이 들어오게 되면 D단자 값이 1이 되고, 다음 상태 값은 1로 변경된다. 언제? Clock이 뛸 때 동기화가 되면서 변경된다.

이 얘기는 Clock만 뛰면 I값에 따라 D 단자 안의 값이 변경된다. 근데 이런 경우만 존재하는게 아니라, 이미 D안에 있는 값들을 유지시키고 싶을 수도 있다. (4번 내용) Clock을 뛰게 만드냐, 뛰지 않게 만드냐를 해주어야하고 그렇지 않으면 밑에 적혀있는대로 Extra control logic을 추가해주어야한다.

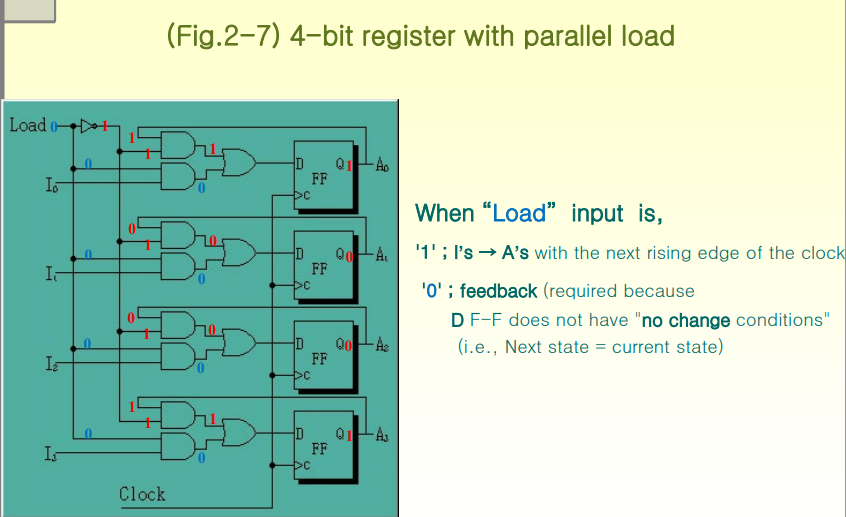

위에서 설명한 Extra Logic : 위 그림에서 보면 빨간색 숫자들이 D안에 있던 수를 유지시키기 위한 Feedback

Load값이 1이었다면, 외부에 있는 I(1,2,3,4)들을 입력값들로 받아서 D F/F에 전달하겠다는 것

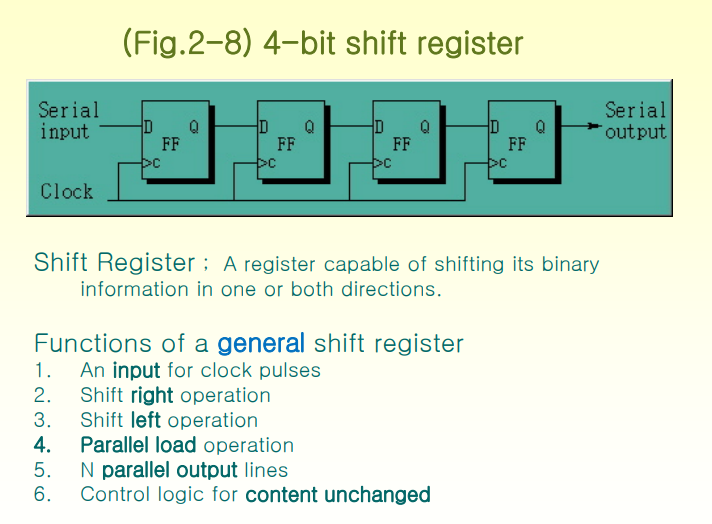

위 그림은 오른쪽으로 Shift시킬 수 있는 기능을 가지고 있다. (1->2) (2->3) (3->4) (4->외부)

shift register는 clock에 신호값에 의해 동기화 되면서 실행

일반적인 general shift register는 여섯 가지 기능을 다 할 수 있어야 한다.

1. clock신호값이 들어올 수 있어야한다. 위 그림에서 F/F와 Clock이 연결되어있는 것을 의미

2,3. 왼쪽/오른쪽으로 shift operation할 수 있어야한다.

4. Parallel load : 초기값이 그대로 Parallel하게 해당되는 F/F으로 들어갈 수 있어야한다

5. Shift Register 안에 있는 값들을 다 외부로 뽑아내서 확인할 수 있어야한다.

6. 들어가 있는 값 그대로 유지

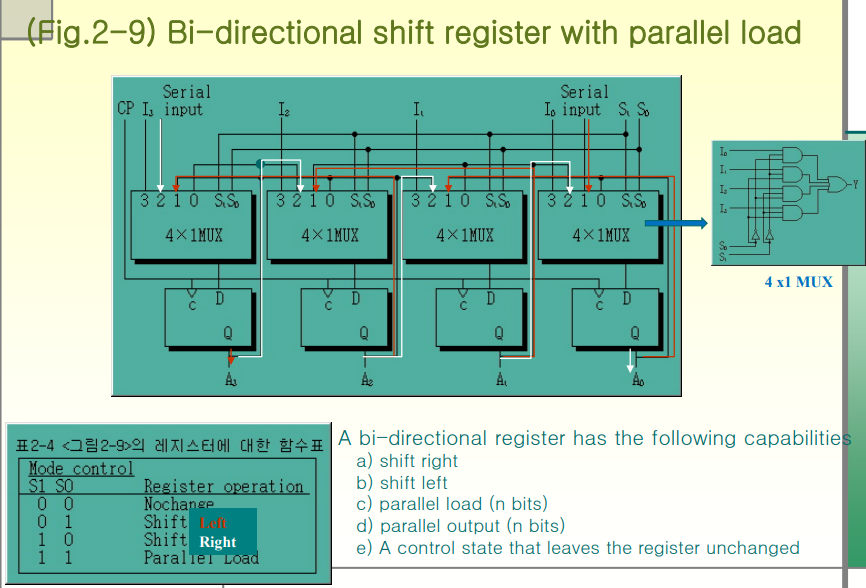

parallel output에 해당되는 내용은 4개 F/F안에 있는 값을 밖으로 꺼낼 수 있어야한다. 위 그림에서 Mux와 F/F가 연결되어있는 데 A신호를 뽑아서 확인할 수 있다.

가운데 들어가는 것은 4x1 mux 이므로 4개 중에 하나(0,1,2,3)를 선택해서 그 채널로 들어오는 값을 출력으로 연결시켜주겠구나. (4x1 mux) 이것을 4개 사용 ; 구조는 오른쪽에 있음 Select는 2개 필요

위 그림에서 보면 Select bit s1, s2가 모두 다 똑같은 값이 물려있다. "이 얘기는 어느 한 4x1 mux가 0번 채널을 하나 선택했다? 그럼 나머지 mux도 다 0번 채널을 선택한다." 라는 것을 의미

D F/F을 사용 ? 무엇을 떠올려야하냐

Clock이 뛸 때 무조건 D단자에 물려있는 값을 받아서 다음 상태를 그 값으로 결정. 지금 가지고 있는 값을 유지하고 싶다면 전 슬라이드에서 배운 한 번 Feedback되서 이미 들어가있던 값이 한 바퀴 돌아서 D단자에 물리도록 해주어야한다.

Function Table

s1, s2 = 0 (0번 채널 선택): 다음 4x1 mux도 다 0번 채널 선택, 0번 채널을 위에서 보면 출력된 값과 입력값으로 들어가기 전 값이 feedback형태로 연결되어있다 => 원래 들어가있던 값 그대로 유지

s1 = 0, s2 = 1 : 1번 채널 선택, 오른쪽 D F/F값이 왼쪽 1번 채널과 연결 => 오른쪽 D F/F에 있던 값이 왼쪽으로 이동

맨 오른쪽에 있던 F/F에 있던 값은 외부에서 들어온다. 1번 채널 보면 Serial Input이라고 되어있음, 외부에서 들어온 값이 1번 채널을 통과해서 D 단자로 연결이 되고 0이면 다음상태 0, 1이면 다음상태 1

s1 = 1, s2 = 0 : 2번 채널 선택, 왼쪽에 있는 F/F값이 오른쪽으로 가서 4x1 mux 2번 채널로 들어가서 그게 D F/F으로 이동 => 왼쪽에서 오른쪽으로 이동. 맨 왼쪽에 있는 4x1 mux에 외부의 값이 들어오게 되면 그 값이 D F/F값이 되고, 동시에 그 안에 있던 값은 하나 오른쪽으로 밀려간 거고, 또 역시 하나 더 오른쪽으로, 가다가 맨 오른쪽은 D F/F에 있던 값은 바깥으로 빠져나간다.

s1 = 1, s2 = 1: 3번 채널 선택, 외부에서 들어온 값 그대로 D F/F에 들어감, 아까 살펴본 특성, 원하는 값을 미리 넣어주고 나서 shift operation을 하고 싶을 때 parallel load특성을 사용하면 된다.

특성, parallel output은 어느 한 순간에 각각의 F/F안에 들어있는 값을 외부로 뽑아낼 수 있으면 된다. 위 그림 F/F에 Q와 연결되어있는 A값들